東京--(BUSINESS WIRE)--(ビジネスワイヤ) -- キオクシア株式会社は、3次元フラッシュメモリにおける円型メモリセルのゲート電極を分断して半円型にすることでセルサイズを縮小し、高集積化を実現するセル構造「Twin BiCS FLASH」を開発しました。セルの設計においてチャージトラップ型の電荷蓄積層ではなく、導電体の電荷蓄積層(フローティングゲート)を用いることで、従来の円型セルよりも小さいセルサイズで、高い書込スロープと広い書込・消去ウィンドウを取得することに世界で初めて1成功しました。また、この新規構造のセルは、大容量化に有効なセルの超多値化に応用が可能であることを実証しました。本成果は、米国サンフランシスコで開催されているIEEEの電子素子に関する国際学会IEDM(International Electron Devices Meeting)にて、12月11日(現地時間)に発表しました。

これまで、BiCS FLASHTMなどの3次元フラッシュメモリでは、セルの積層数を増やすことで、大容量化を実現しています。しかし、セルの積層数が100層を超え、高アスペクト比の加工が難しくなってきています。そこで、従来の円型セルのゲート電極を分断して半円型にすることでセルサイズを縮小し、より少ないセルの積層数で高いビット密度を実現する技術を開発しました。

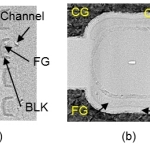

円型セルはフラットセルと比較して、曲率効果により書込ウィンドウを確保し、書込飽和2を抑制できます。今回提案するセル構造は、曲率効果の利点を生かせる半円形状を採用し、さらに電荷蓄積層は電荷の捕獲効率が高い導電体、ブロック膜にはリーク電流を下げるための高誘電率絶縁体を用いています(図1)。これにより、円型セルに比べて高い書込スロープと広い書込・消去ウィンドウを、縮小したセルサイズにて実証しました(図2)。また、これらの特性改善技術により、セルサイズを縮小した半円型セルでVt分布のシミュレーションを行うと、従来の円型セルと同等の4ビット/セル(Quadruple-Level Cell)でのVt分布、さらに低トラップのシリコンチャネルを組み合わせることで5ビット/セル(Penta-Level Cell)でのVt分布が確認できました(図3)。これにより大容量化に有効なセルの超多値化に有望な構造であることがわかりました。

当社は今後も本技術の実用化に向けて研究開発を進めていきます。また、当社はフラッシュメモリの研究開発を積極的に行っており、今回のIEDMでは他に6件の論文発表を行います。

1 2019年12月12日現在、当社調べ

2 印加電圧あたりの閾値電圧変動量が減少する特性

*本文に掲載の製品名やサービス名は、それぞれ各社が商標として使用している場合があります。

Contacts

本資料に関するお問い合わせ先:

キオクシアホールディングス株式会社

広報部

山路 航太

Tel: 03-6478-2319

kioxia-hd-pr@kioxia.com